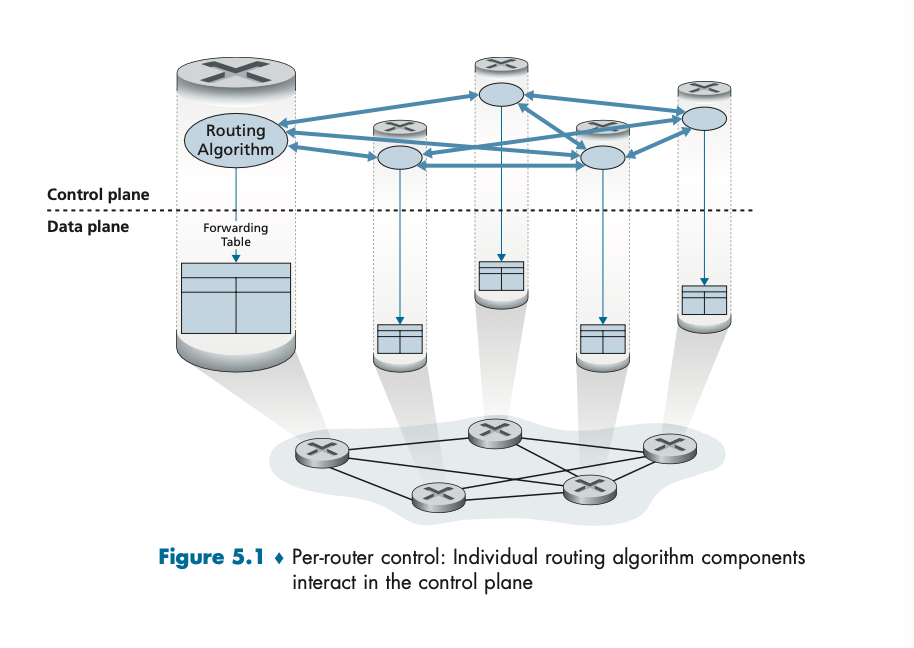

데이터 평면과 제어 평면의 역할 • 데이터 평면(Data Plane): 패킷이 네트워크를 통해 전달되는 동안 “포워딩” 작업을 수행하는 구간. • 제어 평면(Control Plane): 어떤 경로를 따라 패킷을 전달할지를 결정하는 작업. 주요 개념 요약: • 포워딩 테이블: 라우터 내부의 데이터 평면에서 사용되는 테이블로, 특정 목적지로 가는 패킷을 어디로 전달해야 할지 지정합니다. • 플로우 테이블: 소프트웨어 정의 네트워킹(SDN) 환경에서 패킷의 행동을 정의하는 일반화된 테이블입니다. 제어 방식 1. 라우터 단위 제어 (Per-router Control) • 라우팅 알고리즘이 각 라우터마다 독립적으로 실행됩니다. • 라우터는 서로 통신하여 최적 경로를 계산하고 포워딩 테이블을 작성합니다. • 예..